## High Efficiency DC/DC Power Module

**MPN12AD06-TS**

#### **FEATURES:**

- High Power Density Power Module

- Standard DOSA footprint

- Maximum Load:6A

- Input Voltage Range from 4.5V to 16.0V

- Output Voltage Range from 0.6V to 5.5V

- 97% Peak Efficiency

- Voltage Mode Control

- Protections (OCP, UVP, OTP, Non-latching)

- Internal Soft Start

- Pre-Biased Output

- Fixed Switching Frequency of 600k Hz

- Power Good Indication

- Small size and low profile (12.19mm x 12.19mm x 5.4mm)

- Negative / Positive on/off logic

- Pb-free Available (RoHS compliant)

- MSL 2a, 245°C Reflow

- Compliant to IPC-9592 (September 2008)

#### **APPLICATIONS:**

- General Buck DC/DC Conversion

- DC Distributed Power System

- Telecom and Networking Equipments

- Servers System

#### **GENERAL DESCRIPTION:**

The MPN12AD06-TS is a high frequency, high power density and complete DC/DC power module. The PWM controller, power MOSFETs and most of support components are integrated in one hybrid package. Additional, a new patent technology is adopted to stack power choke on the hybrid module in order to achieve high power density.

The features of MPN12AD06-TS include voltage mode control with high phase margin compensation, internal soft start, protections, and pre-biased output function. Besides, MPN12AD06-TS is an easy to use DC/DC power module, it only needs input/output capacitors and one voltage dividing resistor to perform properly.

The low profile and compact size enables utilization of space on the top of PC boards either for highly density point of load regulation to save the space and area. It is suitable for automated assembly by standard surface mount equipment and complies with Pb-free and RoHS compliance.

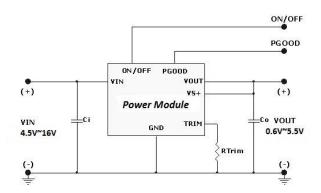

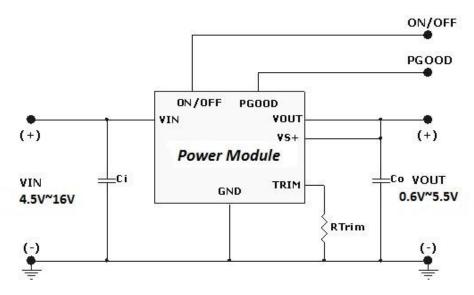

#### **TYPICAL APPLICATION CIRCUIT & PACKAGE SIZE:**

FIG.1 TYPICAL APPLICATION CIRCUIT

FIG.2 HIGH DENSITY POWER MODULE

# High Efficiency DC/DC Power Module

MPN12AD06-TS

## **ORDER INFORMATION:**

| Part Number  | Ambient Temp. Range<br>(°C) | Package<br>(Pb-Free) | MSL      | Note |

|--------------|-----------------------------|----------------------|----------|------|

| MPN12AD06-TS | -40 ~ +85                   | QFN                  | Level 2a | -    |

| Order Code   | Packing       | Quantity |

|--------------|---------------|----------|

| MPN12AD06-TS | Tape and reel | 450      |

This product is not recommended for second (back) side reflow.

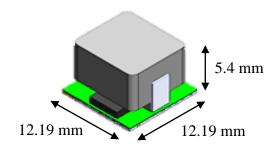

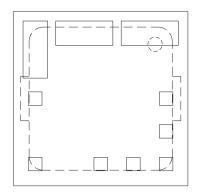

## **PIN CONFIGURATION:**

**BOTTOM VIEW**

# High Efficiency DC/DC Power Module

MPN12AD06-TS

## PIN DESCRIPTION:

| Symbol     | Pin No. | Description                                                                                                                                                                                                                                                             |

|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ON/OFF     | 1       | Enable – to pull the pin lower than 0.8V or floating Disable – pull the pin higher than 3.0V                                                                                                                                                                            |

| VIN        | 2       | Power input pin. It needs to be connected to input rail. It also needs to be connected to thermal dissipation layer by vias connection.                                                                                                                                 |

| GND        | 3、7     | All voltage levels are referenced to the pins. All pins should be connected together with a ground plane                                                                                                                                                                |

| VOUT       | 4       | Power output pin. It needs to be connected to output rail. It also needs to be connected to thermal dissipation layer by vias connection.                                                                                                                               |

| VS+(SENSE) | 5       | Output voltage sensing pin. Connect to output loading to eliminate the positive voltage loss along the trace and keep the regulation at loading. CAUTION: Do not leave this pin open.                                                                                   |

| TRIM       | 6       | Feedback input. Connect a resistor between this pin and ground for adjusting output voltage. Place this resistor as closely as possible to this pin and ground.                                                                                                         |

| NC         | 8 \ 9   | No connect                                                                                                                                                                                                                                                              |

| PGOOD      | 10      | This is an open drain signal and pulls low when any condition exists that would indicate that the output of the supply might be out of regulation. An external pull-up resistor ( $1k\sim50$ kohm) should be connected to a supply +5V, if not use leave this pin open. |

## **ELECTRICAL SPECIFICATIONS:**

CAUTION: Do not operate at or near absolute maximum rating listed for extended periods of time. This stress may adversely impact product reliability and result in failures outside of warranty.

| Parameter                        | Description                                         | Min. | Тур. | Max.  | Unit |

|----------------------------------|-----------------------------------------------------|------|------|-------|------|

| ■ Absolute Maximum Ratings       |                                                     |      |      |       |      |

| VIN to GND                       | Continuous                                          | -0.3 | -    | +18.0 | V    |

| ON/OFF to GND                    |                                                     | -0.3 | -    | +10.7 | V    |

| VS+ to GND                       |                                                     | -0.3 | -    | +7.0  | V    |

| TRIM to GND                      |                                                     | -0.3 | -    | +7.0  | V    |

| PGOOD to GND                     |                                                     | -0.3 | -    | +7.0  | V    |

| Tc                               |                                                     | -    | -    | +110  | °C   |

| Tj                               |                                                     | -40  | -    | +125  | °C   |

| Tstg                             |                                                     | -40  | -    | +125  | °C   |

| Reflow peak temperature          |                                                     | -    | -    | 260   | °C   |

|                                  | Human Body Model (HBM)                              | -    | -    | 2k    | V    |

| ESD Rating                       | Machine Model (MM)                                  | -    | -    | 100   | V    |

|                                  | Charge Device Model (CDM)                           | -    | -    | 1k    | V    |

| ■ Thermal Information            | ation                                               | 1    | 1    | 1     | 1    |

| Rth(jchoke-a)                    | Thermal resistance from junction to ambient. Note 1 | -    | 25   | -     | °C/W |

| Recommendation Operating Ratings |                                                     |      |      |       |      |

| VIN                              | Input Supply Voltage                                | +4.5 | _    | +16.0 | V    |

| VOUT                             | Adjusted Output Voltage                             | +0.6 | -    | +5.5  | V    |

| Та                               | Ambient Temperature                                 | -40  | -    | +85   | °C   |

#### NOTES:

<sup>1.</sup> Rth(jchoke-a) is measured with the component mounted on an effective thermal conductivity test board on 0 LFM condition. The test board size is  $80 \text{mm} \times 80 \text{mm} \times 1.6 \text{mm}$  with 4 layers, 1 oz per layer. The test condition is complied with JEDEC EIJ/JESD 51 Standards.

## **ELECTRICAL SPECIFICATIONS: (Cont.)**

Conditions:  $T_A = 25$  °C, unless otherwise specified. Vin=12V, Vout=3.3V, Cin=22uF/Ceramic×3, Cout=47uF/Ceramic×2 + POScap LOW ESR 330uF (6TPE330ML)

| Symbol                                        | Parameter                                    | Conditions                                                                      | Min.  | Тур.  | Max.  | Unit    |

|-----------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------|-------|-------|-------|---------|

| ■ Inpu                                        | t Characteristics                            |                                                                                 |       |       |       |         |

| ${ m I}_{ m IN}$                              | Input supply bias current                    | Iout = 0A<br>Vin = 12V, Vout = 3.3V                                             | -     | 40    | -     | mA      |

| Is                                            | Input supply current                         | Iout = 6A<br>Vin = 12V, Vout = 3.3V                                             | -     | 1.75  | -     | А       |

| ■ Outp                                        | ut Characteristics                           |                                                                                 |       |       |       |         |

| $I_{\text{OUT(DC)}}$                          | Output continuous current range              | Vin=12V, Vout=3.3V                                                              | 0     | -     | 6     | А       |

| $\Delta$ Vout/ $\Delta$ Vin                   | Line regulation accuracy                     | Vin = 10.8V to 13.2V<br>Vout = 3.3V, Iout = 0A<br>Vout = 3.3V, Iout = 6A        | -     | 0.3   | -     | %       |

| $\Delta V_{\text{OUT}}/\Delta I_{\text{OUT}}$ | Load regulation accuracy                     | Iout = 0A to 6A<br>Vin = 12V, Vout = 3.3V                                       | -     | 0.5   | -     | %       |

| $V_{\text{OUT(AC)}}$                          | Output ripple voltage                        | Iout = 6A<br>Vin = 12V, Vout = 3.3V                                             | -     | 20    | 30    | mVp-p   |

| Vo, set                                       | Output voltage set point                     | TJ = 25°C, with 0.5% tolerance for external resistor used to set output voltage | -1.0  | -     | +1.0  | %V0,set |

| Coesr                                         | ESR limitation of<br>Output capacitor        |                                                                                 | 10    | 25    | 50    | mΩ      |

| Co                                            | Output capacitance value                     |                                                                                 | 300   | -     | 3000  | uF      |

| ■ Dyna                                        | amic Characteristi                           | CS                                                                              |       |       |       |         |

| $\Delta V_{	ext{OUT-DP}}$                     | Voltage change for positive load step        | Iout = 3A to 6A<br>Current slew rate = 2.5A/uS<br>Vin = 12V, Vout = 3.3V        | -     | 50    | 75    | mVp-p   |

| $\Delta V_{	ext{OUT-DN}}$                     | Voltage change for negative load step        | Iout = 3A to 6A<br>Current slew rate = 2.5A/uS<br>Vin = 12V, Vout = 3.3V        | -     | 50    | 75    | mVp-p   |

| ■ Cont                                        | rol Characteristics                          | S                                                                               |       |       |       |         |

|                                               | D. C                                         | TJ = 25°C                                                                       | 0.597 | 0.6   | 0.603 | .,      |

| $V_{REF}$                                     | Reference voltage                            | -40°C < TJ < 125°C                                                              | 0.594 | 0.6   | 0.606 | V       |

| Fosc                                          | Oscillator frequency                         |                                                                                 | 540   | 600   | 660   | kHz     |

| $V_{UV}$                                      | Feedback lower<br>voltage limit for<br>PGOOD |                                                                                 | 0.500 | 0.525 | 0.550 | V       |

| $V_{\text{OV}}$                               | Feedback upper<br>voltage limit for<br>PGOOD |                                                                                 | 0.655 | 0.675 | 0.700 | V       |

| ${ m I}_{ m PGL}$                             | PGOOD pulldown current                       | R <sub>PGOOD</sub> =1K, V <sub>BIAS</sub> =5V                                   | -     | -     | 5     | mA      |

| $V_{PGL}$                                     | PGOOD pulldown<br>Voltage                    | I <sub>PGOOD</sub> =5mA,                                                        | -     | -     | 0.4   | V       |

## **ELECTRICAL SPECIFICATIONS: (Cont.)**

Conditions:  $T_A = 25$  °C, unless otherwise specified. Vin=12V, Vout=3.3V, Cin=22uF/Ceramic×3, Cout=47uF/Ceramic×2 + POScap LOW ESR 330uF (6TPE330ML)

| Symbol           | Parameter                              | Conditions                                  | Min. | Тур. | Max. | Unit |  |

|------------------|----------------------------------------|---------------------------------------------|------|------|------|------|--|

| ■ ON-0           | OFF Control, (Nega                     |                                             |      |      |      |      |  |

| Von/off          | Logic Low Voltage                      | Module On                                   | -    | -    | 0.8  | V    |  |

| Von/off          | Logic High Voltage                     | Module Off                                  | 3.0  | -    | -    | V    |  |

| Ton(Delay)       | Output delay time                      | EN=high to low, Vout = 90%<br>Setting point | 9.3  | -    | 17   | ms   |  |

| ■ Effici         | ency                                   |                                             |      |      |      |      |  |

| η                | Efficiency                             | VIN=12V, VOUT=1.0V, IOUT=6A                 | -    | 86   | -    | %    |  |

| η                | Efficiency                             | VIN=12V, VOUT=1.2V, IOUT=6A                 | -    | 87.7 | -    | %    |  |

| η                | Efficiency                             | VIN=12V, VOUT=1.8V, IOUT=6A                 | -    | 91   | -    | %    |  |

| η                | Efficiency                             | VIN=12V, VOUT=2.5V, IOUT=6A                 | -    | 93   | -    | %    |  |

| η                | Efficiency                             | VIN=12V, VOUT=3.3 V, IOUT=6A                | ı    | 94.3 | -    | %    |  |

| η                | Efficiency                             | VIN=12V, VOUT=5V, IOUT=6A                   | -    | 95.7 | -    | %    |  |

| ■ PWM            |                                        |                                             |      |      |      |      |  |

| Dмах             | Maximum duty cycle                     |                                             | 90   | -    | -    | %    |  |

| TON(min)         | Minimum<br>controllable pulse<br>width |                                             | -    | -    | 70   | ns   |  |

| ■ Fault          | ■ Fault Protection                     |                                             |      |      |      |      |  |

| T <sub>SD</sub>  | Shutdown temperature                   | Tj of internal PWM IC.                      | -    | 145  | -    | ℃    |  |

| T <sub>SDH</sub> | Hysteresis                             |                                             | -    | 20   | -    | °C   |  |

| ■ Othe           | Other Characteristics                  |                                             |      |      |      |      |  |

| L                | Inductance                             |                                             | -    | 1    | -    | uН   |  |

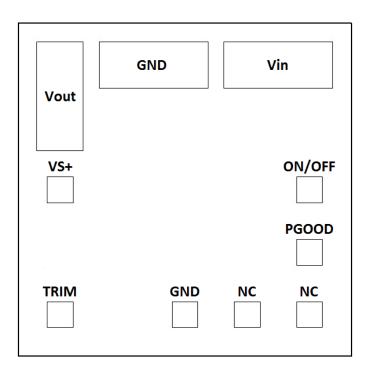

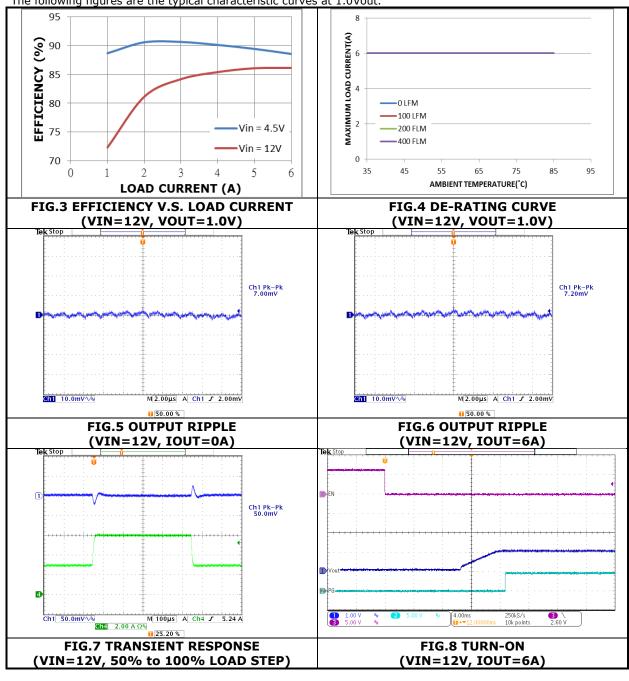

## TYPICAL PERFORMANCE CHARACTERISTICS: (VOUT=1.0V)

Conditions:  $Cin=22uF/Ceramic\times3$ ,  $Cout=47uF/Ceramic\times2 + POScap LOW ESR 330uF (6TPE330ML)$ . Test Board Information:  $80mm\times80mm\times1.6mm$ , 4 layers.

#### NOTES:

The output ripple and transient response are measured by short loop probing and limited to 20MHz bandwidth. The following figures are the typical characteristic curves at 1.0Vout.

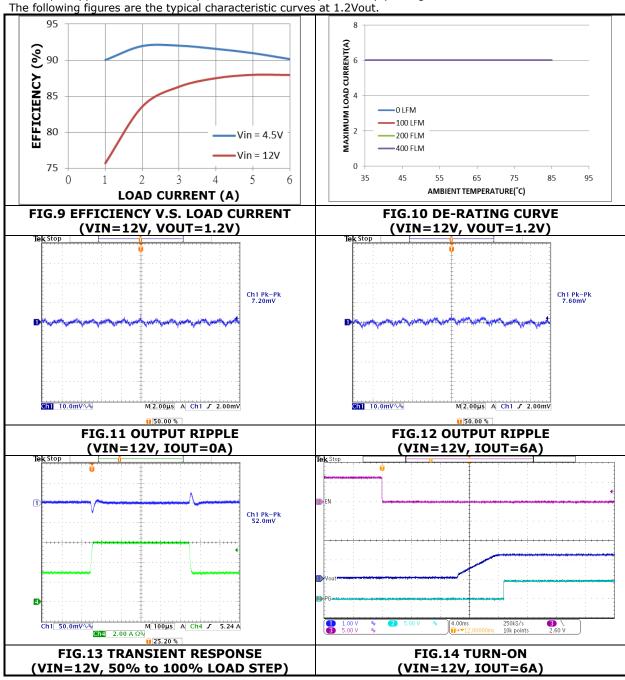

## TYPICAL PERFORMANCE CHARACTERISTICS: (VOUT=1.2V)

Conditions:  $Cin=22uF/Ceramic\times3$ ,  $Cout=47uF/Ceramic\times2 + POScap LOW ESR 330uF (6TPE330ML)$ . Test Board Information:  $80mm\times80mm\times1.6mm$ , 4 layers.

#### NOTES:

The output ripple and transient response are measured by short loop probing and limited to 20MHz bandwidth.

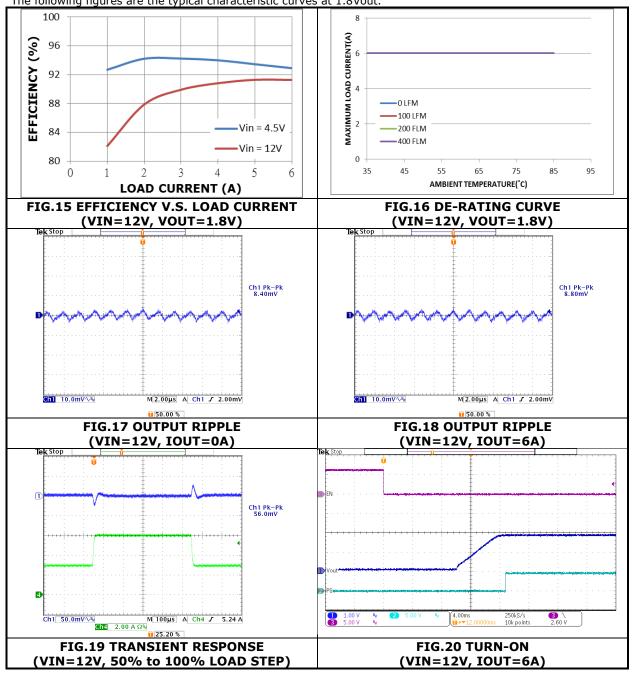

## **TYPICAL PERFORMANCE CHARACTERISTICS: (VOUT=1.8V)**

Conditions:  $Cin=22uF/Ceramic\times3$ ,  $Cout=47uF/Ceramic\times2 + POScap LOW ESR 330uF (6TPE330ML)$ . Test Board Information:  $80mm\times80mm\times1.6mm$ , 4 layers.

#### NOTES:

The output ripple and transient response are measured by short loop probing and limited to 20MHz bandwidth. The following figures are the typical characteristic curves at 1.8Vout.

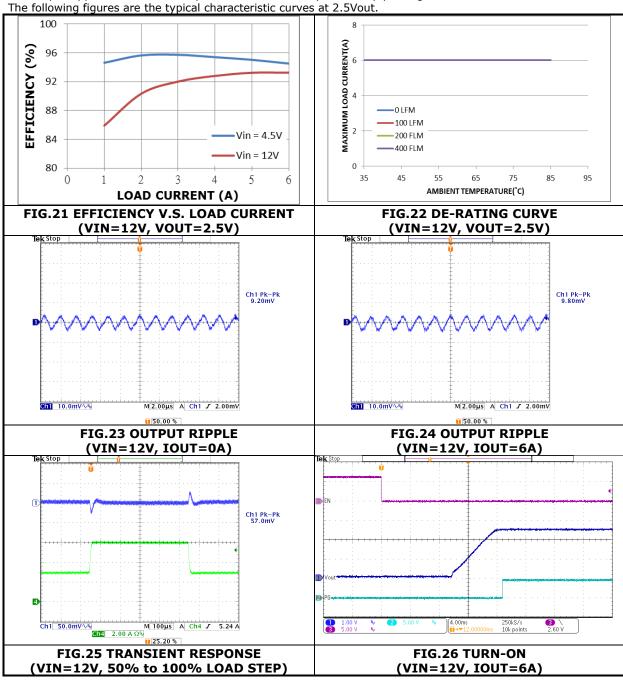

## **TYPICAL PERFORMANCE CHARACTERISTICS: (VOUT=2.5V)**

Conditions:  $Cin=22uF/Ceramic\times3$ ,  $Cout=47uF/Ceramic\times2 + POScap LOW ESR 330uF (6TPE330ML)$ . Test Board Information:  $80mm\times80mm\times1.6mm$ , 4 layers.

#### NOTES:

The output ripple and transient response are measured by short loop probing and limited to 20MHz bandwidth.

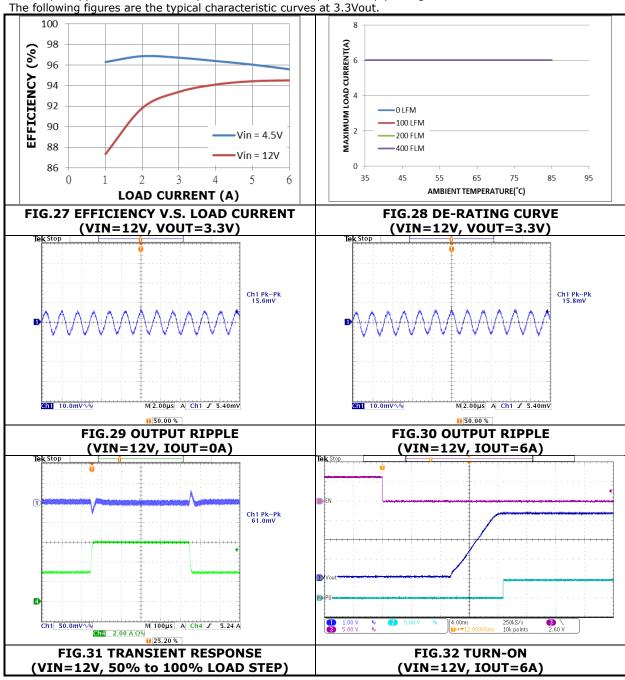

## **TYPICAL PERFORMANCE CHARACTERISTICS: (VOUT=3.3V)**

Conditions:  $Cin=22uF/Ceramic\times3$ ,  $Cout=47uF/Ceramic\times2 + POScap LOW ESR 330uF (6TPE330ML)$ . Test Board Information:  $80mm\times80mm\times1.6mm$ , 4 layers.

#### NOTES:

The output ripple and transient response are measured by short loop probing and limited to 20MHz bandwidth.

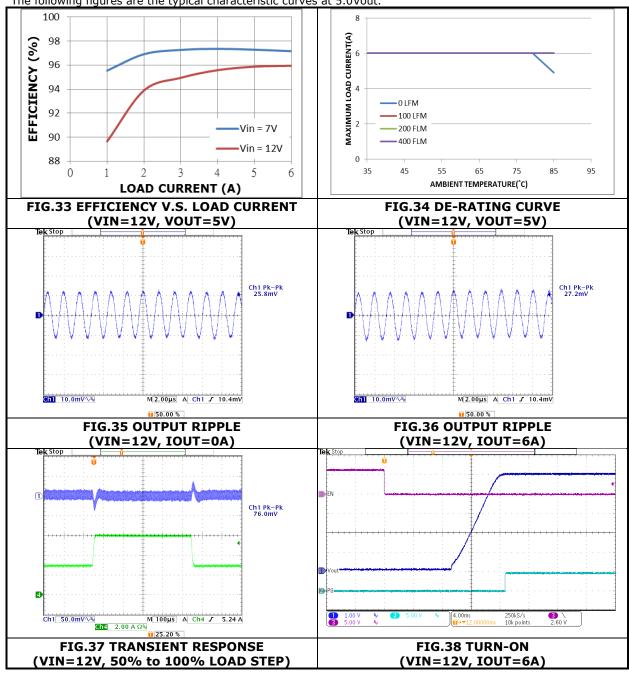

## **TYPICAL PERFORMANCE CHARACTERISTICS: (VOUT=5V)**

Conditions:  $Cin=22uF/Ceramic\times3$ ,  $Cout=47uF/Ceramic\times2 + POScap LOW ESR 330uF (6TPE330ML)$ . Test Board Information:  $80mm\times80mm\times1.6mm$ , 4 layers.

#### NOTES:

The output ripple and transient response are measured by short loop probing and limited to 20MHz bandwidth. The following figures are the typical characteristic curves at 5.0Vout.

## **APPLICATIONS INFORMATION:**

#### REFERENCE CIRCUIT FOR GENERAL APPLICATION:

The FIG.39 shows the MPN12AD06-TS application schematics for input voltage +12V. Condition:

$VIN = 12V \ , \ VOUT = 1.8V \ , \ IOUT = 6A$   $Ci1 = 3 \times 22uF \ / \ 25V \ , \ Co1 = 330uF \ / \ 6.3V \ (6TPE330ML) \ , \ Co2 = 2 \times 47uF \ / \ 6.3V$   $RTrim = 5k \ ohm$

FIG.39 TYPICAL APPLICATION CIRCUIT

#### **SAFETY CONSIDERATION:**

Certain applications and/or safety agencies may require fuses at the inputs of power conversion components. Fuses should also be used when there is the possibility of sustained input voltage reversal which is not current limited. For greatest safety, we recommend a fast blow fuse installed in the ungrounded input supply line. The installer must observe all relevant safety standards and regulations. For safety agency approvals, install the converter in compliance with the end-user safety standard.

#### **INPUT FILTERING:**

The module should be contacted to as low AC impedance source supply and a highly inductive source or line inductance can affect the stability of the module. An input capacitor must be placed directly to the input pin of the module, to minimize input ripple voltage and ensure module stability.

#### **OUTPUT FILTERING:**

To reduce output ripple and improve the dynamic response to as step load change, the additional capacitor at the output must be used. Low ESR polymer and ceramic capacitors are recommended to improve the output ripple and dynamic response of the module.

#### PRE-BIAS STARTUP:

The MPN12AD06-TS contains a circuit to prevent current from being pulled from the output during startup in the condition the output is pre-biased. There are on PWM pulses until the internal soft-start voltage rises above the error amplifier input, if the output is pre-biased. Once the soft-start voltage exceeds the error amplifier input, the controller slowly initiates synchronous rectification by starting the synchronous rectifier with narrow on time. It then increments that on time on a cycle-by-cycle basis until it coincides with the time dictated by (1-D), where the D is duty cycle of the converter. This approach prevents the sinking of current from a pre-biased output, and ensures the output voltage startup and ramp to regulation is smooth and controlled.

#### **POWER GOOD:**

The MPN12AD06-TS provides an indication that output is good for the converter. This is an open drain signal and pulls low if any condition exists such as VTRIM is more than +/- 12.5% from nominal, soft-start is active, and short circuit condition has been detected. The PGOOD terminal should be connected through a pull up resistor to a source of 5VDC. When there is no power to the device, PGOOD is not able to pull close to GND if an auxiliary supply is used for the power good indication. In this case, the PGOOD pin look approximately like a diode to GND.

#### **OVERCURRENT PROTECTION:**

The over-current function protects the converter from a shorted output by using the low side MOSFET on-resistance,  $R_{DS(ON)}$ , to monitor the current. When the protection is triggered, the module enters hiccup mode. The module operates normally once the fault is removed.

#### **OVER TEMPERATURE PROTECTION:**

If the junction temperature of the MPN12AD06-TS reaches the thermal shutdown limit of  $145^{\circ}$ C, the PWM and the oscillator are turned off and H/L MOSFET are driven low. When the junction cools to the required level ( $125^{\circ}$ C typical), the PWM initiates soft start as during a normal power up cycle.

#### **REMOTE SENSE:**

The power module has a Remote Sense feature to eliminate the distribution losses on the output line trace and keep the regulation at loading point. In the event of an open remote sense line, the module shall maintain local sense regulation through an internal resistor.

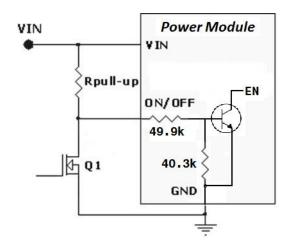

#### **REMOTE ON/OFF:**

The MPN12AD06-TS power module has an ON/OFF pin for remote ON/OFF operation. Both positive and negative ON/OFF logic options are available.

For negative logic, the circuit configuration is shown in FIG.40. To turn the module OFF, Q1 should be turned OFF and voltage of ON/OFF pin should be pull-high with an external pull-up resistor. To turn the module ON, Q1 is turned ON to have voltage of ON/OFF pin pull-low.

#### FIG.40 CIRCUIT FOR NEGATIVE ON/OFF LOGIC

$$V_{\text{ON/OFF}} = V_{\text{IN}} \times \left( \frac{49.9 \text{ K} + 40.3 \text{ K}}{R_{\text{pull}-up} + 49.9 \text{ K} + 40.3 \text{ K}} \right) \qquad 3 \text{ V} < V_{\text{ON/OFF}} < 10.7 \text{ V}$$

(EQ.1)

#### **OUTPUT VOLTAGE PROGRAMMING:**

The MPN12AD06-TS has an internal 0.6V reference voltage, It only programs the dividing resistor  $R_{TRIM}$  which respects to TRIM pin and GND, and division resistor needs to be closed as possible to the TRIM pin. The output voltage can be calculated as shown in Equation 1 and the resistance according to typical output voltage is shown in TABLE 1. (Note: internal resistance was 10k ohm  $\pm$  0.5%)

$$VOUT = 0.6 \times \left(1 + \frac{10k}{R_{TRIM}}\right)$$

(EQ.2)

| VOUT       | 1.0V | 1.2V | 1.5V   | 1.8V | 2.5V   | 3.3V   | 5V     |

|------------|------|------|--------|------|--------|--------|--------|

| RTrim(ohm) | 15k  | 10k  | 6.667k | 5k   | 3.158k | 2.222k | 1.364k |

TABLE 1

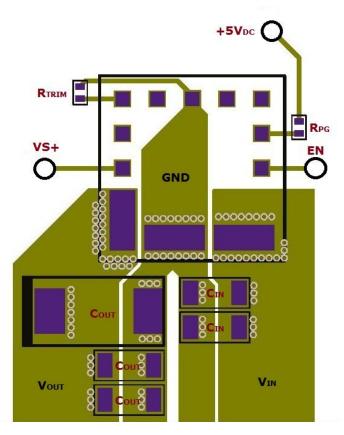

#### **RECOMMENDATION LAYOUT GUIDE:**

FIG.41 RECOMMENDATION LAYOUT (TOP LAYER)

#### **THERMAL CONSIDERATIONS:**

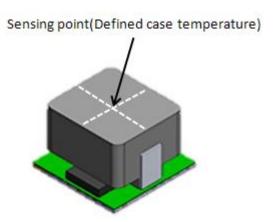

All of thermal testing condition is complied with JEDEC EIJ/JESD 51 Standards. Therefore, the test board size is  $80 \text{mm} \times 80 \text{mm} \times 1.6 \text{mm}$  with 4 layers. The case temperature of module sensing point is shown as FIG.42. Then Rth( $j_{\text{choke-a}}$ ) is measured with the component mounted on an effective thermal conductivity test board on 0 LFM condition. The MPN12AD06-TS module is designed for using when the case temperature is below 110°C regardless the change of output current, input/output voltage or ambient temperature.

FIG.42 CASE TEMPERATURE SENSING POINT

#### **REFLOW PARAMETERS:**

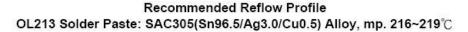

Lead-free soldering process is a standard of making electronic products. Many solder alloys like Sn/Ag, Sn/Ag/Cu, Sn/Ag/Bi and so on are used extensively to replace traditional Sn/Pb alloy. Here the Sn/Ag/Cu alloy (SAC) are recommended for process. In the SAC alloy series, SAC305 is a very popular solder alloy which contains 3% Ag and 0.5% Cu. It is easy to get it. FIG.43 shows an example of reflow profile diagram. Typically, the profile has three stages. During the initial stage from 70°C to 90°C, the ramp rate of temperature should be not more than 1.5°C/sec. The soak zone then occurs from 100°C to 180°C and should last for 90 to 120 seconds. Finally the temperature rises to 230°C to 245°C and cover 220°C in 30 seconds to melt the solder. It is noted that the time of peak temperature should depend on the mass of the PCB board. The reflow profile is usually supported by the solder vendor and user could switch to optimize the profile according to various solder type and various manufactures' formula.

FIG.43 RECOMMENDATION REFLOW PROFILE

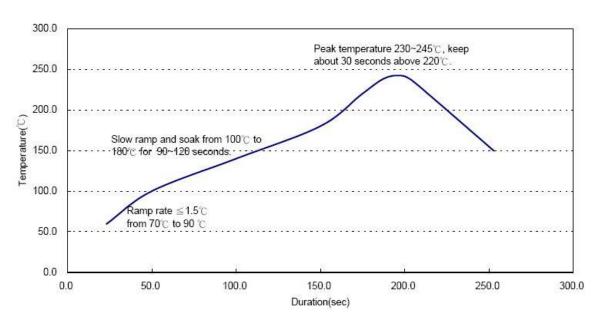

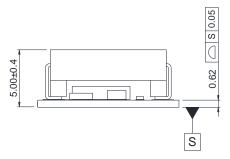

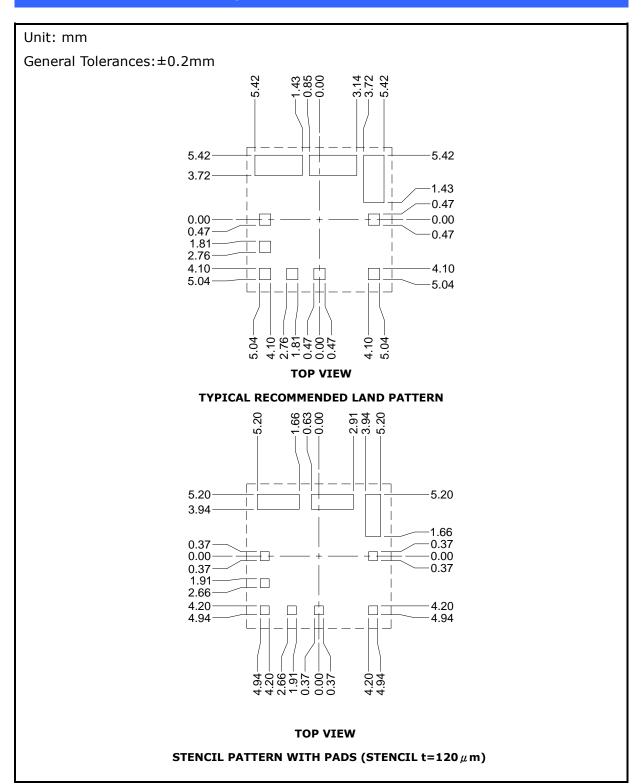

## **PACKAGE OUTLINE DRAWING:**

Unit: mm

General Tolerances: ±0.2mm

Solder Pad: ENIG(Electroless Nickel Immersion Gold)

**TOP VIEW**

**BOTTOM VIEW**

SIDE VIEW

## **LAND PATTERN REFERENCE:**

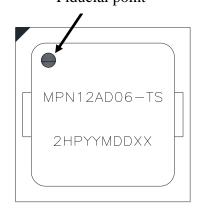

## **MARKING DRAWING:**

## Fiducial point

**TOP VIEW**

**BOTTOM VIEW**

## Marking note:

- 1. Circle represents the fiducial point of SMT

- 2. MPN12AD06-TS represents the Product Name

- 3. 2HPYYMDDXX represents the Lot Number

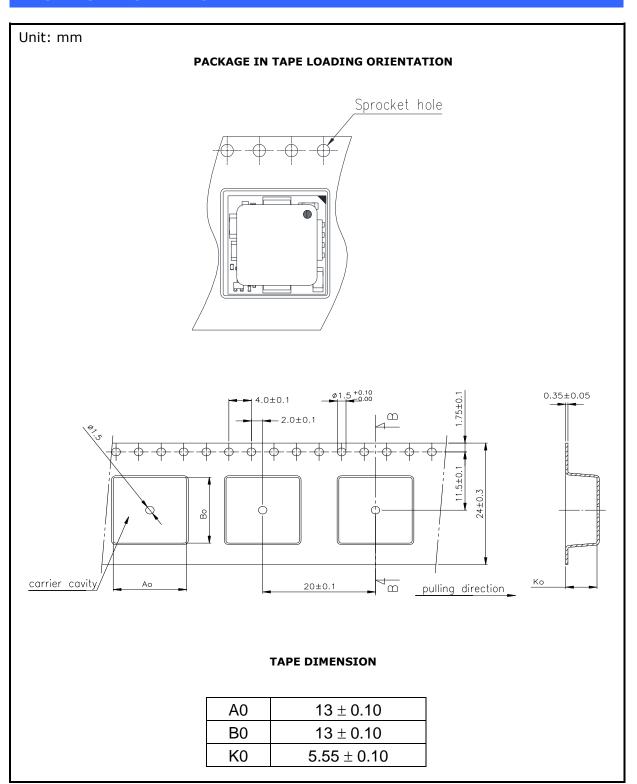

## **PACKING INFORMATION:**

## **PACKING INFORMATION: (Cont.)**

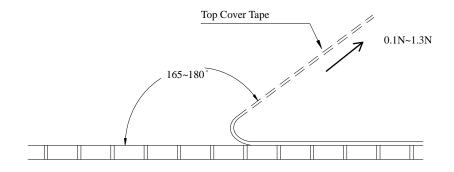

## **Peel Strength of Top Cover Tape**

The peel speed shall be about 300mm/min.

The peel force of top cover tape shall be between 0.1N to 1.3N

## **REVISION HISTORY:**

| Date               | Revision | Changes                                                           |

|--------------------|----------|-------------------------------------------------------------------|

| 2014.06.17         | 00       | Release the preliminary specification.                            |

| 2014.10.24         | 01       | Adding POD, packing information.                                  |

| 2014 12 05         | 0.2      | Change output range, adding pinout description and test           |

| 2014.12.05         | 02       | condition information.                                            |

|                    |          | 1. PACKAGE OUTLINE DRAWING                                        |

|                    |          | Add Tolerances ±0.2mm                                             |

| 2014.12.17         | 03       | ● END VIEW Hmax. 5.4 -> 5±0.4                                     |

|                    |          | 2. PACKING INFORMATION                                            |

|                    |          | ● TAPE DIMENSION K0=5.25±0.10 ->5.55±0.10                         |

| 2015.01.06         | 04       | Add MARKING DRAWING                                               |

| 2015.02.04         | O.E.     | PACKING INFORMATION                                               |

| 2015.02.04         | 05       | PIN 1 , Top left corner -> Top right corner                       |

|                    |          | 1. Thermal Considerations:                                        |

|                    |          | Add Thermal Considerations                                        |

|                    |          | Add Case Temperature Sensing Point                                |

|                    |          | 2. PACKAGE OUTLINE DRAWING                                        |

|                    |          | Tolerances:±0.2mm -> General Tolerances:±0.2mm                    |

| 2015.02.26         | 06       | Modify Drawing                                                    |

| 2013.02.20         | 00       | 3. LAND PATTERN REFERENCE                                         |

|                    |          | Add General Tolerances ±0.2mm                                     |

|                    |          | Modify Drawing                                                    |

|                    |          | 4. PACKING INFORMATION:                                           |

|                    |          | Modify TAPE Drawing                                               |

|                    |          | 5. Update electrical specifications and applications information  |

|                    |          | 1. Change MSL level from level 2a to level 2                      |

| 2015.04.24         | 07       | 2. Change Output voltage set point tolerance from $\pm 2\%$ to    |

| 2013:07:2 <b>T</b> |          | $\pm 1\%$ and added output ripple and dynamic characteristics MAX |

|                    |          | values                                                            |

| 2015.05.22         | A0       | 1. Change MSL level from level 2 to level 2a                      |

## **REVISION HISTORY:(Cont.)**

|            |     | 1. Change page 5 ON / OFF Pin description                                   |

|------------|-----|-----------------------------------------------------------------------------|

| 2015.10.22 | A1  | 2. Add page 15 RECOMMENDATION LAYOUT GUIDE                                  |

|            |     | 3. Add page 17 REFLOW PARAMETERS                                            |

| 2016.01.22 | ۸.2 | 1. Update page 1 GENERAL DESCRIPTION                                        |

| 2016.01.22 | A2  | 2. Update page 18 · 20 · 21 pin 1 mark of PCB base                          |

|            |     | 1. Change page 4 ON/OFF pin MAX. rating from +7V to +10.7V                  |

|            |     | 2. Change page 5 ON/OFF, Module On Logic Low Voltage, Module                |

|            |     | Off Logic High Voltage                                                      |

| 2016 00 20 | 4.2 | 3. Replace page 5 I <sub>on/off</sub> information for customer to calculate |

| 2016.09.29 | А3  | accordingly by page 15 equation EQ.1 with updated REMOTE                    |

|            |     | ON/OFF and FIG.40                                                           |

|            |     | 4. Replace page 21~22 circle marking name Pin 1 by fiducial                 |

|            |     | point                                                                       |

| 2010 02 22 | 0.4 | Add page 5 output capacitor Characteristics and page 6                      |

| 2018.03.23 | A4  | inductance information                                                      |

|            |     | 1 · Add page 4 peak reflow temperature                                      |

|            |     | 2 · Add page 5 PGOOD characteristic                                         |

|            |     | 3 · Add page 6 turn-on output delay time                                    |

|            |     | 4 · Update page 7~12 waveform of turn-on                                    |

| 2019.05.28 | A5  | 5 · Update page 14 information of Power Good                                |

|            |     | 6 · Add page 19 Solder Pad: ENIG(Electroless Nickel Immersion               |

|            |     | Gold)                                                                       |

|            |     | 7 · Update page 20 stencil pattern with square pads to stencil              |

|            |     | pattern with pads.                                                          |

| 2020 12 1  | 4.5 | Page 2 add "This product is not recommended for second (back) side          |

| 2020.10.14 | A6  | reflow" information.                                                        |

| L          |     |                                                                             |